### **JDEP 284H**

**Foundations of Computer Systems**

## Processor Architecture V: Making the Pipelined Implementation Work

Dr. Steve Goddard goddard @cse.unl.edu

http://cse.unl.edu/~goddard/Courses/JDEP284

## Giving credit where credit is due

- Most of slides for this lecture are based on slides created by Dr. Bryant, Carnegie Mellon University.

- I have modified them and added new slides.

2

## Overview

### Make the pipelined processor work!

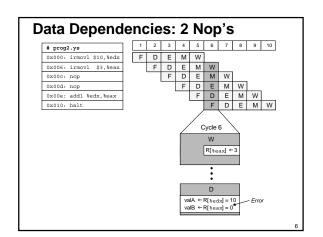

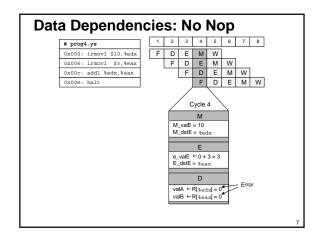

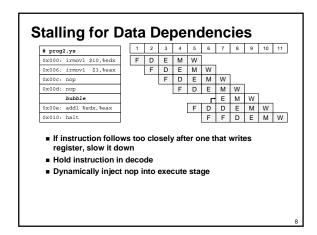

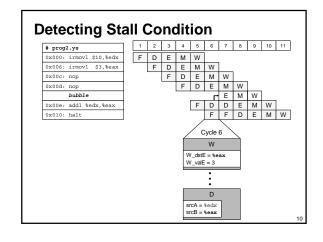

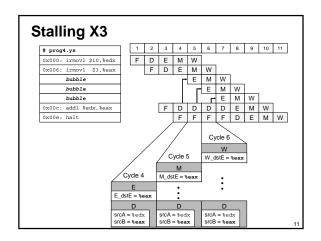

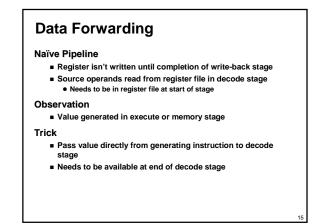

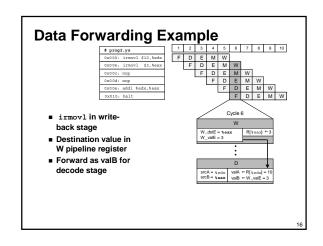

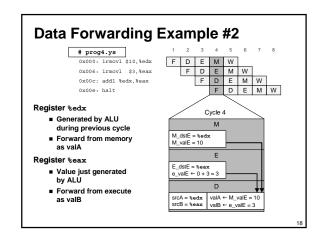

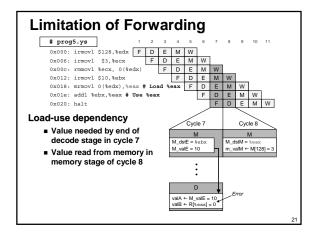

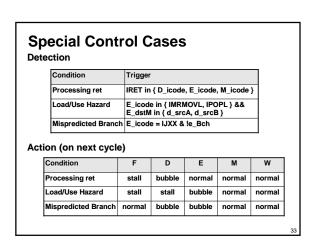

### **Data Hazards**

- Instruction having register R as source follows shortly after instruction having register R as destination

- Common condition, don't want to slow down pipeline

### **Control Hazards**

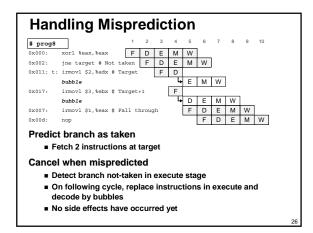

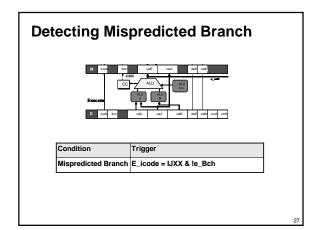

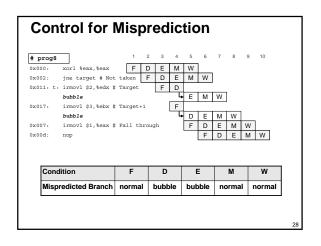

- Mispredict conditional branch

- Our design predicts all branches as being taken

- Naïve pipeline executes two extra instructions

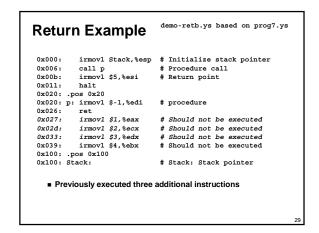

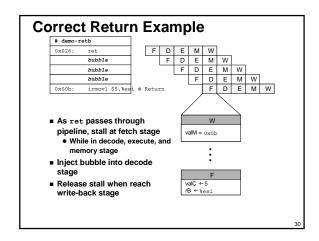

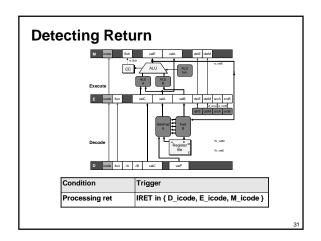

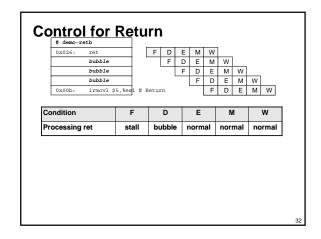

- Getting return address for ret instruction

- Naïve pipeline executes three extra instructions

### Making Sure It Really Works

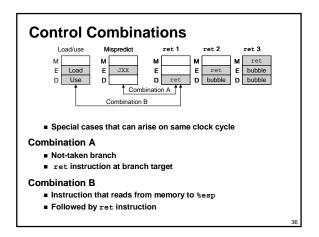

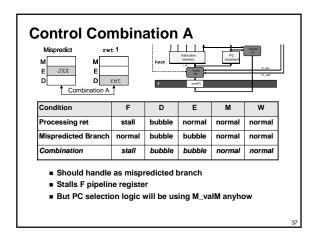

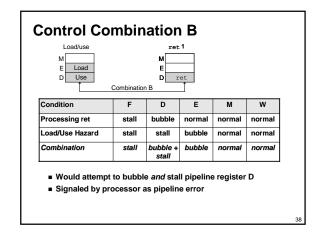

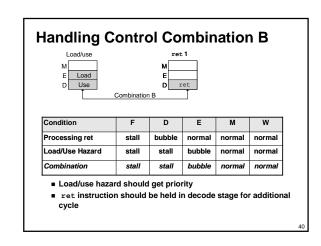

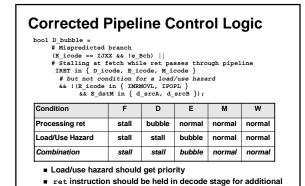

■ What if multiple special cases happen simultaneously?

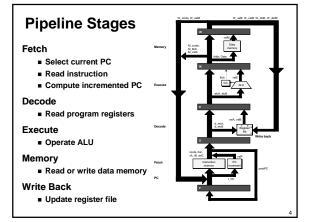

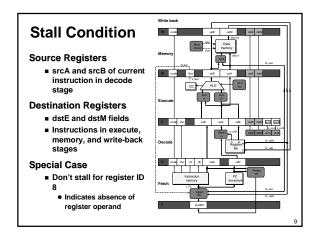

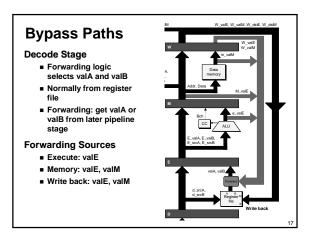

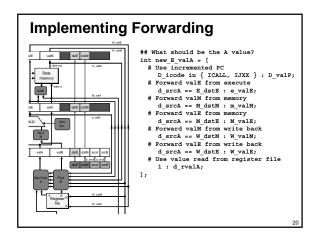

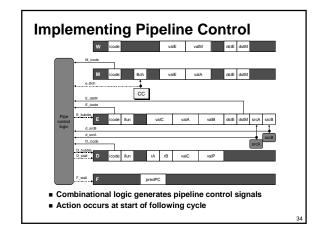

# PIPE- Hardware Pipeline registers hold intermediate values from instruction execution Forward (Upward) Paths Values passed from one stage to next Cannot jump past stages e.g., valC passes through decode

### **Branch Misprediction Example** prog8.ys with 3 nop's inserted xorl %eax,%eax 0x000: 0x002: ine t # Not taken irmovl \$1, %eax # Fall through 0x00d: nop nop 0x00f: nop 0x010: 0x010: hard 0x011: t: irmovl \$3, %edx 0x017: irmovl \$4, %ecx 0x01d: irmovl \$5, %edx # Target (Should not execute) # Should not execute # Should not execute ■ Should only execute first 7 instructions

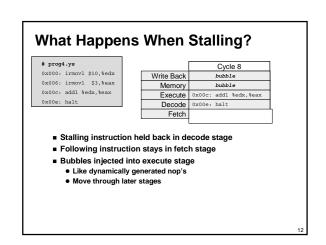

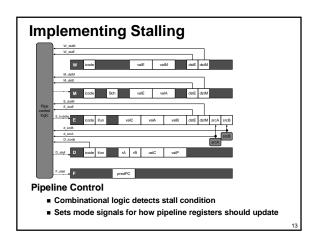

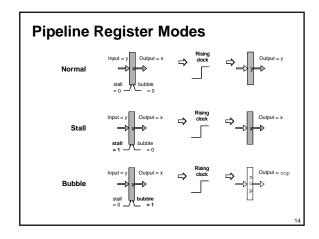

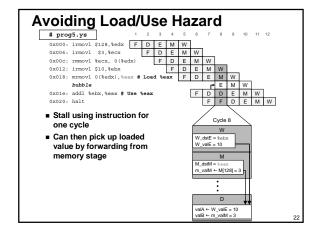

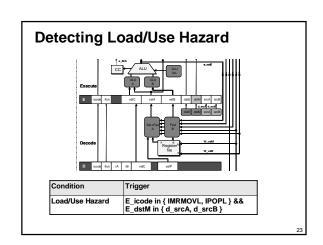

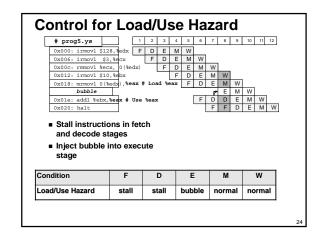

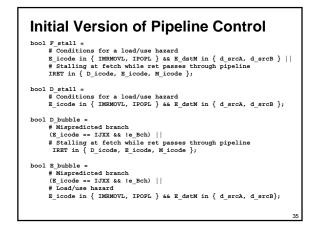

## Pipeline Summary Data Hazards Most handled by forwarding No performance penalty Load/use hazard requires one cycle stall Control Hazards Cancel instructions when detect mispredicted branch Two clock cycles wasted Stall fetch stage while ret passes through pipeline Three clock cycles wasted Control Combinations Must analyze carefully First version had subtle bug Only arises with unusual instruction combination